データセンターの DDR5 への移行は、他のアップグレードよりも重要である可能性があります。しかし、多くの人は、DDR5 は DDR4 を完全に置き換えるための移行にすぎないと漠然と考えています。DDR5 の登場によりプロセッサーは必然的に変更され、いくつかの新しいプロセッサーが追加される予定です。メモリ前世代の DRAM の SDRAM から SDRAM へのアップグレードの場合と同様に、DDR4.

ただし、DDR5 は単なるインターフェイスの変更ではなく、プロセッサ メモリ システムの概念を変えています。実際、DDR5 への変更は、互換性のあるサーバー プラットフォームへのアップグレードを正当化するのに十分である可能性があります。

新しいメモリ インターフェイスを選択する理由は何ですか?

コンピュータの出現以来、コンピューティングの問題はより複雑になり、この必然的な増加により、サーバーの数の増加、メモリとストレージの容量の増加、プロセッサのクロック速度とコア数の増加という形で進化が推進されましたが、同時にアーキテクチャの変化も推進されました。 、これには、最近の細分化されて実装された AI 技術の採用が含まれます。

すべての数値が上昇しているため、これらすべてが並行して起こっていると考える人もいるかもしれません。ただし、プロセッサ コアの数は増加していますが、DDR 帯域幅が追いついていないため、コアあたりの帯域幅は実際には減少しています。

特に HPC、ゲーム、ビデオ コーディング、機械学習推論、ビッグ データ分析、データベースなどのデータ セットが拡大しているため、CPU にメモリ チャネルを追加することでメモリ転送の帯域幅を改善できますが、消費電力は増加します。 。プロセッサのピン数もこのアプローチの持続可能性を制限しており、チャネル数は永久に増加することはできません。

一部のアプリケーション、特に GPU や特殊な AI プロセッサなどのハイコア サブシステムは、一種の高帯域幅メモリ (HBM) を使用します。このテクノロジーは、スタックされた DRAM チップから 1024 ビット メモリ レーンを介してプロセッサにデータを実行するため、AI などのメモリを大量に使用するアプリケーションにとって優れたソリューションになります。これらのアプリケーションでは、高速転送を実現するためにプロセッサとメモリをできるだけ近くに配置する必要があります。ただし、価格も高く、交換/アップグレード可能なモジュールにチップを搭載することはできません。

また、今年広く展開され始めた DDR5 メモリは、アップグレード可能性をサポートしながら、プロセッサとメモリ間のチャネル帯域幅を向上させるように設計されています。

帯域幅と遅延

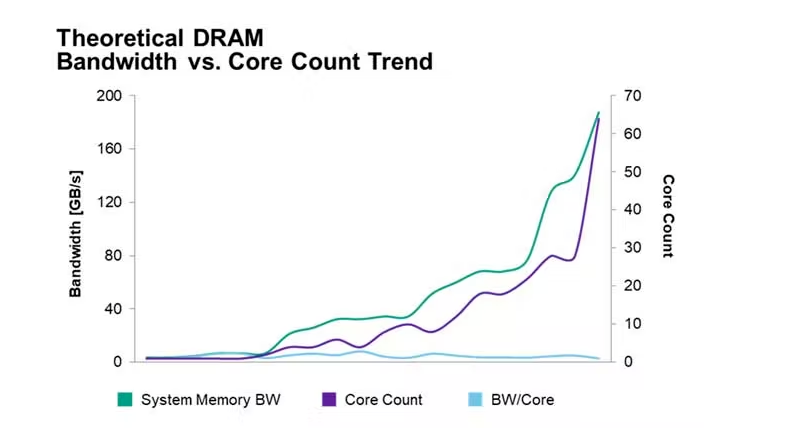

DDR5 の転送速度は、前世代の DDR よりも高速です。実際、DDR4 と比較すると、DDR5 の転送速度は 2 倍以上です。DDR5 では、単純なゲインを超えてこれらの転送速度でのパフォーマンスを可能にする追加のアーキテクチャ変更も導入されており、観測されたデータ バス効率が向上します。

さらに、バースト長が BL8 から BL16 に 2 倍になり、各モジュールが 2 つの独立したサブチャネルを持つことが可能になり、システム内で使用可能なチャネルが実質的に 2 倍になりました。転送速度が向上するだけでなく、転送速度が高くなくても DDR4 を上回る再構築されたメモリ チャネルも得られます。

DDR5 への移行により、メモリ集約型のプロセスが大幅に強化され、今日のデータ集約型ワークロードの多く、特に AI、データベース、オンライン トランザクション処理 (OLTP) がこの説明に当てはまります。

通信速度も非常に重要です。DDR5 メモリの現在の速度範囲は 4800 ~ 6400MT/s です。テクノロジーが成熟するにつれて、伝送速度はさらに高くなることが予想されます。

エネルギー消費

DDR5 は DDR4 よりも低い電圧、つまり 1.2V ではなく 1.1V を使用します。8% という違いはそれほど大きくないように聞こえるかもしれませんが、電力消費率を計算するためにこれらを 2 乗すると、その違いは明らかです。つまり、1.1 平方/1.2 平方 = 85 %、つまり電気代が 15 % 節約されることになります。

DDR5 によって導入されたアーキテクチャの変更により、帯域幅の効率が最適化され、転送速度が向上しますが、これらの数値は、テクノロジが使用される正確なアプリケーション環境を測定せずに定量化するのが困難です。しかし、繰り返しになりますが、アーキテクチャの改善と転送速度の向上により、エンド ユーザーはデータ ビットあたりのエネルギーの向上を感じるでしょう。

さらに、DIMM モジュール自体で電圧を調整することもできるため、マザーボードの電源調整の必要性が軽減され、さらなる省エネ効果が得られます。

データセンターの場合、サーバーが消費する電力と冷却コストが懸念されます。これらの要素を考慮すると、よりエネルギー効率の高いモジュールとしての DDR5 がアップグレードの理由となることは間違いありません。

エラー訂正

DDR5 にはオンチップ エラー訂正も組み込まれており、DRAM プロセスが縮小し続けるにつれて、多くのユーザーはシングル ビット エラー率と全体的なデータ整合性の増加を懸念しています。

サーバー アプリケーションの場合、オンチップ ECC は、DDR5 からデータを出力する前に、読み取りコマンド中のシングル ビット エラーを修正します。これにより、ECC の負担の一部がシステム修正アルゴリズムから DRAM にオフロードされ、システムの負荷が軽減されます。

DDR5 ではエラー チェックとサニタイズも導入されており、有効にすると、DRAM デバイスは内部データを読み取り、修正されたデータを書き戻します。

要約する

通常、DRAM インターフェイスはデータセンターがアップグレードを実装する際に最初に考慮する要素ではありませんが、DDR5 テクノロジーはパフォーマンスを大幅に向上させながら電力を節約することが約束されているため、詳しく検討する価値があります。

DDR5 は、早期採用者が将来の構成可能でスケーラブルなデータ センターにスムーズに移行できるようにするテクノロジーです。IT およびビジネス リーダーは、データセンター変革計画を完了するために、DDR5 を評価し、DDR4 から DDR5 に移行する方法と時期を決定する必要があります。

投稿日時: 2022 年 12 月 15 日